|

Цифровой сигнальный процессорЦифровой сигнальный процессор (англ. digital signal processor, DSP, цифровой процессор обработки сигналов (ЦПОС)) — специализированный микропроцессор, предназначенный для обработки оцифрованных сигналов (обычно, в режиме реального времени)[1].   Особенности архитектурыАрхитектура сигнальных процессоров, по сравнению с микропроцессорами общего применения, имеет некоторые особенности, связанные со стремлением максимально ускорить выполнение типовых задач цифровой обработки сигналов, таких, как цифровая фильтрация, преобразование Фурье, поиск сигналов и т. п. Математически эти задачи сводятся к поэлементному перемножению элементов многокомпонентных векторов действительных чисел, последующему суммированию произведений (например, в цифровой фильтрации выходной сигнал фильтра с конечной импульсной характеристикой равен сумме произведений коэффициентов фильтра на вектор выборок сигнала, аналогичные вычисления производятся при поиске максимумов корреляционных и автокорелляционных функций выборок сигналов). Поэтому сигнальные процессоры оптимизированы по быстродействию для выполнения именно таких операций. И ЦСП ориентированы, в первую очередь, на многократное выполнение умножения с расчётом «на лету» адресов перемножаемых элементов массивов:

Ограниченность аппаратных ресурсов первых ЦСП накладывала существенный отпечаток на их архитектуру:

В современной микроэлектронике процессоры общего применения зачастую содержат аппаратную поддержку типовых операций ЦОС. Особо времяёмкие задачи ЦОС решаются на основе программируемой логики, где можно достичь предельной оптимизации выполнения конкретной операции. Специализированные процессоры ЦОС всё чаще делают векторными. В то же время классические ЦСП снабжают развитыми наборами команд процессоров общего применения и сглаживают особенности программной модели, позиционируя их как изделия широкого применения с ускоренными функциями ЦОС. Все эти тенденции приводят к размыванию классического понятия ЦСП. Области применения

ИсторияПредшествующие разработкиДо 1980 года несколько компаний выпустили устройства, которые можно считать предшественниками ЦСП. Так, в 1978 Intel выпускает «процессор аналоговых сигналов» 2120. В его состав входили АЦП, ЦАП и процессор обработки цифровых данных, однако аппаратная функция умножения отсутствовала. В 1979 AMI выпускает S2811 — периферийное устройство, управляемое основным процессором компьютера. Оба изделия не достигли успеха на рынке. Первое поколение (начало 1980-х)Основную историю ЦСП принято отсчитывать от 1979—1980 годов, когда Bell Labs представила первый однокристальный ЦСП Mac 4, а также на «IEEE International Solid-State Circuits Conference '80» были показаны µMPD7720[англ.] компании NEC и DSP1[англ.] компании AT&T, которые, однако, не получили широкого распространения. Стандартом де-факто стал выпущенный чуть позже кристалл TMS32010[англ.] фирмы Texas Instruments, по многим параметрам и удачным техническим решениям превосходящий изделия конкурентов. Вот некоторые его характеристики:

Второе поколение (середина 1980-х)Благодаря прогрессу в полупроводниковых технологиях в этот период были выпущены изделия, имеющие расширенные функции по сравнению с первым поколением. К характерным отличиям можно отнести:

Много позднее также были выпущены устройства, формально относящиеся ко второму поколению, но имеющие следующие усовершенствования:

Третье поколение (конец 1980-х)Третье поколение ЦСП принято связывать с началом выпуска изделий, реализующих арифметику с плавающей запятой. Характерные особенности первых выпущенных образцов:

Четвёртое поколениеЧетвёртое поколение ЦСП характеризуется значительным расширением наборов команд, созданием VLIW и суперскалярных процессоров. Заметно возросли тактовые частоты. Так, например, время выполнения команды MAC (Y := X + A × B) удалось сократить до 3 нс. Современные ЦСПЛучшие современные ЦСП можно характеризовать следующими параметрами:

Основные параметры ЦСП

Часто используются также интегральные характеристики ЦСП, например, показатель «мощность/ток/быстродействие», например, ma/MIPS (миллиампер на 1 млн инструкций в секунду), что позволяет оценить реальную потребляемую мощность в зависимости от сложности задачи, решаемой процессором в указанный момент. Выбор ЦСП целиком определяется назначением разрабатываемой системы. Например, для массовых мобильных устройств важна дешевизна процессора, низкое энергопотребление, в то время как стоимость разработки системы отходит на второй план. С другой стороны, для измерительного оборудования, систем обработки звуковой и видеоинформации важны эффективность процессора, наличие развитых инструментальных средств, многопроцессорность и т. д. Оценка и сравнение производительностиКак отмечено ранее, отдельные характеристики типа тактовой частоты, MIPS, MOPS, MFLOPS позволяют оценить быстродействие ЦСП достаточно неоднозначно. Поэтому для решения задачи измерения и сравнения характеристик разных ЦСП используют специальные наборы тестов, имитирующих некоторые распространённые задачи цифровой обработки сигналов. Каждый тест состоит из нескольких небольших программ, которые пишутся на ассемблере и оптимизируются под заданную архитектуру. Эти тесты могут включать реализацию:

Наиболее авторитетным пакетом тестов на сегодняшний день является тест BTDImark2000 (BDTI DSP Kernel Benchmarks™ (BDTImark2000™) Certified Results), который, кроме указанных алгоритмов, включает также оценку используемой алгоритмом памяти, время разработки системы и другие параметры. УстройствоГарвардская архитектура

Цифровые сигнальные процессоры строятся на основе т. н. «Гарвардской архитектуры», отличительной особенностью которой является то, что программы и данные хранятся в различных устройствах памяти — памяти программ и памяти данных. В отличие от архитектуры фон Неймана, где процессору для выборки команды и двух операндов требуется минимум три цикла шины, ЦСП может производить одновременные обращения как к памяти команд, так и к памяти данных, и указанная выше команда может быть получена за два цикла шины. В реальности, благодаря продуманности системы команд и другим мерам, это время может быть сокращено до одного цикла. В реальных устройствах память команд может хранить не только программы, но и данные. В этом случае говорят, что ЦСП построен по модифицированной гарвардской архитектуре. Память команд и память данных обычно располагаются на кристалле ЦСП. В связи с тем, что эта память имеет относительно небольшой объём, возникает необходимость в использовании внешних (относительно кристалла процессора) запоминающих устройств. Для таких устройств раздельные шины команд и данных не используются, так как это потребовало бы значительно увеличить количество внешних выводов кристалла, что дорого и непрактично. Поэтому взаимодействие ЦСП с внешними запоминающими устройствами происходит по одному комплекту шин без разделения на команды и данные. Обращение к внешней памяти всегда занимает значительно больше времени, чем к внутренней, поэтому в приложениях, критичных ко времени исполнения, такие обращения стараются минимизировать.

Конвейерное исполнение командКонвейер представляет собой вычислительный поток, который на каждой стадии выполняет определённую микрооперацию, поэтому на конвейере в каждый момент времени находится несколько команд на разной стадии выполнения. Это позволяет повысить быстродействие. Наличие нескольких конвейеров реализует суперскалярную архитектуру. При параллельной обработке команд на разных конвейерах максимальный эффект достигается на однотипных командах, не зависящих друг от друга. Если в программе присутствуют команды разного типа, то на конвейере вводятся такты ожидания. Для оптимизации загрузки конвейеров необходимо следующее:

В итоге команды выполняются не в том порядке, в каком их записывал программист. Аппаратная реализация основных функцийУмножителиАппаратный умножитель применяется для сокращения времени выполнения одной из основных операций ЦОС — операции умножения. В процессорах общего назначения эта операция реализуется за несколько тактов сдвига и сложения и занимает много времени, а в DSP благодаря специализированному умножителю — за один командный цикл. Функционально умножители делятся на два вида:

СдвигателиСдвигателем называется как устройство, выполняющее операцию сдвига данных, так и регистр, в котором хранится результат сдвига[3]. С точки зрения выполняемых функций, сдвигатели делятся на:

В обоих случаях структура регистра, хранящего результат сдвига, совпадает со структурой аккумулятора.

Устройства генерации адресаАппаратная организация цикловАЛУАЛУ — блок процессора, который под управлением декодера команд выполняет арифметические и логические преобразования над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером машинного слова. Регистры

Аккумулятор — регистр, предназначенный для сохранения результатов операций. В архитектуре многих ЦСП предусмотрено два аккумулятора, что позволяет повысить скорость выполнения операций, требующих хранения промежуточных результатов. Технически аккумулятор может состоять из нескольких регистров[3]:

Наличие регистра EXT позволяет повысить точность вычисления промежуточных результатов, а также увеличить диапазон хранения значений, не приводящих к переполнению. При сохранении значения аккумулятора в ячейку памяти или в обычный регистр, его значение округляется с учётом стандартной ширины этой ячейки или регистра. С другой стороны, при необходимости, содержимое регистра EXT может быть сохранено отдельно. Способы адресацииПроцессор поддерживает режимы прямой адресации, косвенной адресации с пред- и постинкрементом и специфические для задач цифровой обработки сигналов режимы циклической адресации и адресации с реверсированием бит адреса. Классификация ЦСП по архитектуреПриведённая ниже классификация[3] достаточно условна, так как разнообразие технических решений зачастую не позволяет однозначно отнести каждое конкретное устройство к одному из указанных типов. Поэтому нижесказанное следует скорее использовать как материал для понимания особенностей архитектуры ЦСП, чем для реальной классификации каких-либо изделий. Особенности архитектуры ЦСП удобно рассматривать на примере конкретного алгоритма цифровой обработки данных, например, КИХ-фильтра, выходной сигнал которого можно записать как: , где

Вычисление результата является классическим примером использования операции «умножение с накоплением» — MAC (Y := X + A × B). Стандартные ЦСП На рисунке показано два варианта выполнения команды MAC на стандартном ЦСП. В первом варианте оба операнда хранятся в памяти данных, поэтому на их выборку требуется два такта, то есть время выполнения n сложений равно 2n. Во втором случае один из операндов хранится в памяти программ, поэтому команда исполняется за один такт, и общее время выполнения цикла будет равно n тактов (в реальности для исполнения за один такт MAC должна исполняться внутри специальной команды цикла для исключения повторной выборки самого кода команды, что требует дополнительного такта). Эффективная реализация алгоритма требует использования памяти программ для хранения данных. Одним из вариантов, позволяющим отказаться от использования памяти программ для хранения данных, является применение т. н. «двухпортовой памяти», то есть памяти, имеющей два комплекта входных шин — двух шин адреса и данных. Такая архитектура позволяет произвести одновременное обращение по двум адресам (при этом они должны находиться в разных адресуемых блоках). Данное решение применяется в ЦСП компаний Motorola (DSP56000) и Lucent (DSP1600). При указанной архитектуре повысить производительность можно только увеличением тактовой частоты. Улучшенные стандартные ЦСП«Улучшенные стандартные ЦСП» для повышения производительности системы, по сравнению со стандартными ЦСП, используют следующие методы повышения параллелизма:

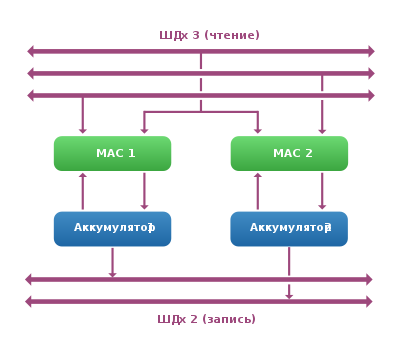

Многие из этих способов применялись уже начиная с самых первых процессоров, поэтому зачастую их невозможно однозначно классифицировать как «стандартные» или «улучшенные».  На рисунке показан пример реализации вычисления двух параллельных команд MAC. Для этого в ЦСП присутствуют два модуля MAC и два аккумулятора. Блоки MAC получают данные по трём шинам одновременно, причём одно из значений является для них общим. Таким образом, происходит одновременное исполнение двух команд:

Особенность показанного решения состоит в том, что к выполнению двух параллельных команд с одним общим сомножителем можно свести многие алгоритмы ЦОС, например:

В некоторых процессорах (Lucent DSP16xxx, ADI ADSP-2116x) используются два одинаковых ядра, каждый со своей памятью, то есть одна команда исполняется одновременно в двух ядрах с различными данными. Это позволяет обойти ограничение на использование полностью независимых данных. Характерным недостатком таких процессоров является необходимость в высокой квалификации разработчика, так как эффективное использование указанных особенностей требует программирования на языке ассемблера, хорошего знания архитектуры и системы команд, то есть эти устройства считаются «недружественными» к языкам высокого уровня. ЦСП с архитектурой VLIWОсновное отличие VLIW-процессоров состоит в том, что коды команд ещё на этапе компиляции собираются в большие «суперкоманды» и выполняются параллельно. Обычно такие процессоры используют RISC-архитектуру с фиксированной длиной команды, где каждая из них выполняется в отдельном операционном модуле. К характерным особенностям таких процессоров можно отнести:

Обычно, если процессор имеет несколько одинаковых модулей, то при создании программы на ассемблере имеется возможность указания только типа необходимого операционного модуля, а конкретное устройство будет назначено компилятором. С одной стороны, это упрощает программирование таких устройств, а с другой стороны, позволяет достаточно эффективно использовать их ресурсы. Суперскалярные ЦСПСуперскалярные процессоры также характеризуются большим набором параллельных операционных модулей и возможностью одновременного исполнения нескольких команд. Однако, по сравнению с VLIW, они имеют две характерные особенности:

С помощью описанного подхода можно обойти следующие недостатки VLIW:

Платой за решение этих проблем становится значительное усложнение схемы процессора, в котором появляется модуль планирования выполнения команд. Суперскалярные процессоры планируют исполнение команд не только на основе информации о загруженности операционных блоков, но и на основе анализа зависимостей между данными. К примеру, команда сохранения результата арифметической операции не может быть выполнена раньше самой операции вычисления, даже если модуль обращения к памяти в данный момент свободен. Эта особенность приводит в том числе к тому, что один и тот же набор команд может по-разному исполняться в различных местах программы, что делает невозможным точную оценку производительности. Особенно это важно для систем, работающих в реальном времени, ведь оценка по наихудшему результату приведёт к тому, что ресурсы процессора будут использованы не полностью. Таким образом, в этих системах задача точной оценки производительности суперскалярных ЦСП остаётся открытой. Гибридные ЦСП Под гибридными ЦСП обычно понимают специализированные устройства, сочетающие в себе функцию микроконтроллера и цифрового сигнального процессора. Обычно такие изделия предназначены для выполнения одной функции — например, управления электрическими двигателями, или другими объектами в реальном времени. Другой широкой областью их применения в последнее время становится мобильная телефония, где ранее использовались два процессора — один обычный для управления функциями аппарата (дисплеем, клавиатурой), а другой для обработки голосовых сигналов (кодирование и т. д.). Классификация ЦСП по назначениюВ целом, по назначению ЦСП можно разделить на две группы:

«Проблемная ориентация» обычно относится не к дополнительным командам, а к набору встроенных специализированных периферийных устройств. Например, ЦСП, предназначенные для управления электродвигателями, могут содержать на кристалле генераторы сигналов ШИМ, контроллеры локальной промышленной сети и т. д. Процессоры, используемые для обработки голосовых сигналов, часто содержат модули манипуляции разрядами (BMU) и сопроцессоры исправления ошибок. В цифровых фото- и видеокамерах применяются ЦСП с модулями кодирования/декодирования MPEG1, MPEG4, JPG, MP3, AAC и др. Программирование ЦСПДля программирования ЦСП обычно используют один из двух языков — ассемблер и C. Основные особенности ассемблеров ЦСП совпадают с аналогичными языками обычных микропроцессоров и, в целом, могут быть описаны как:

С другой стороны, при использовании языков среднего и высокого уровня, в частности, C, можно заметно упростить и ускорить создание программ, но при этом ресурсы системы будут использоваться менее эффективно, по сравнению с программой, целиком написанной на ассемблере. В реальности обычно используется подход, совмещающий достоинства как языков высокого уровня, так и эффективности программ на ассемблере. Выражается это в том, что стандартные библиотеки обычно создаются на ассемблере, как и критичные ко времени исполнения и объёму памяти части кода. В то же время вспомогательные модули могут создаваться на языке высокого уровня, ускоряя и упрощая разработку программной системы в целом. Особенности ассемблеров ЦСПК интересным особенностям ассемблеров ЦСП можно отнести следующее:

Совместимость внутри семейств ЦСПОбычно ЦСП выпускаются семействами, и изделия внутри семейств имеют аналогичные языки ассемблера, или даже совместимы на уровне машинных кодов. Также внутри семейства обычно используются одинаковые наборы библиотек подпрограмм. Как и в обычных микропроцессорах, зачастую старшие модели ЦСП могут исполнять машинный код младших моделей, либо их ассемблер включает все команды младших моделей как подмножество собственного набора команд. Отладка программОбычно отладка программ, написанных для ЦСП, производится с помощью специальных средств, включающих программные имитаторы и эмуляторы. В их состав также часто входят средства профилирования (измерения скорости выполнения блоков кода). Примечания

Литература

|